(transistor de efecto de campo). (Véase TRANSISTOR, FIELD-EFFECT).

Transistores de efecto de campo (FET)

.jpg)

Figura . Símbolos de transistores MOSFET de enriquecimiento (Metal-Oxide-Semiconductor Field-Effect Transistors, MOSFETs). Las fuentes (sources) se indican conectando la flecha central hacia la fuente. Para los nFETs, la flecha apunta hacia adentro (regla nemotécnica: n es “in”). Las compuertas (gates) están representadas por una placa de capacitor, lo que indica que la compuerta sólo está conectada capacitivamente al resto del transistor, es decir, no existe conexión de corriente continua.

La línea discontinua que representa el canal se utiliza para indicar transistores FET de modo de enriquecimiento (enhancement-mode FETs), que son el único tipo que se analiza en ésta página.

Los transistores de efecto de campo (field-effect transistors, FETs) son dispositivos electrónicos de tres terminales ampliamente utilizados para controlar corrientes en aplicaciones como motores, altavoces y sistemas de iluminación. Los más comunes son los MOSFETs (metal-oxide-semiconductor field-effect transistors), que funcionan como interruptores controlados por tensión.

A diferencia de los transistores bipolares, los FETs son dispositivos controlados por tensión y presentan una alta impedancia de entrada.

En los MOSFETs, la compuerta está aislada eléctricamente del canal mediante una capa de óxido, formando una estructura equivalente a un capacitor. Esto permite controlar el canal sin que circule corriente significativa hacia la compuerta.

Existen dos tipos principales de MOSFET: nFET y pFET. En los nFET, los portadores de carga son electrones, mientras que en los pFET son huecos. Además, estos dispositivos incluyen un diodo interno (body diode) debido a la estructura del semiconductor.

El funcionamiento del FET se basa en la modulación de un canal conductor entre source y drain. Cuando la tensión Vgs (entre compuerta y fuente) supera un cierto umbral, se forma un canal que permite el paso de corriente. A mayor tensión en la compuerta, mayor será la corriente de conducción.

En aplicaciones prácticas, los FETs pueden modelarse mediante resistencias controladas por tensión. Por ejemplo, la resistencia entre drenador y fuente (Rds) varía según la tensión Vgs. Este comportamiento es clave en circuitos de amplificación y conmutación.

Las mediciones experimentales muestran que la resistencia del canal disminuye al aumentar la tensión de compuerta. Sin embargo, en la práctica, factores como resistencias parásitas, conexiones y limitaciones del circuito afectan los resultados.

Para obtener mediciones más precisas, se utilizan técnicas de corrección que compensan los errores introducidos por cables, contactos y resistencias adicionales del sistema de medición.

El análisis de los FETs también incluye su comportamiento en diferentes regiones de operación. En la región activa, el transistor permite el control de corriente, mientras que en la región de corte no conduce, y en la región de saturación actúa como un interruptor cerrado.

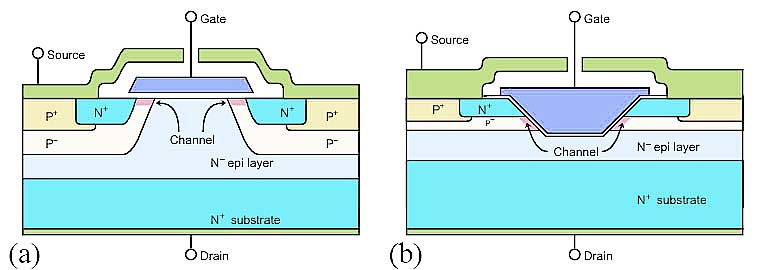

Figura . Estas secciones transversales (cross sections) de un nFET de potencia (power nFET) muestran la compuerta (gate) en color naranja y las conexiones de fuente (source) y drenador (drain) en azul. La región blanca que separa la compuerta de la fuente es un aislante de alta calidad (high-quality insulator), como el dióxido de silicio.

El canal (channel) es la delgada región verde que conecta el semiconductor tipo P cercano a la compuerta. Cuando la compuerta es suficientemente positiva, los huecos son repelidos de la región y los electrones son atraídos hacia ella, formando un canal conductor desde la región N+ de la fuente hacia la región N− y las regiones N+ del drenador. Tensiones de compuerta más altas hacen que el canal sea más grueso, reduciendo así su resistencia.

El diodo interno (body diode) se forma entre la región tipo P y la capa epitaxial tipo N−, y se mantiene polarizado en inversa por las conexiones de fuente y drenador tipo P+ y N+.

En estos diagramas, la capa epitaxial N+ (N+ substrate) debería ser mucho más gruesa para representar correctamente la escala real.

La figura (a) muestra una celda de un VD-MOS power nFET, mientras que la figura (b) muestra una celda de un V-groove nFET.

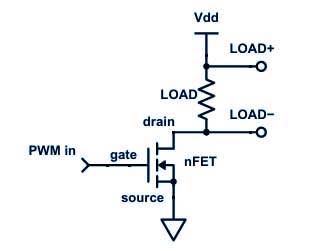

Figura . Un nFET (nFET) puede utilizarse para proporcionar conmutación de alta corriente (high-current switching) a partir de una señal de nivel lógico proveniente de un microcontrolador (microcontroller). La resistencia en conducción (on-resistance, Ron) del nFET debe ser mucho menor que la resistencia de la carga (Rload), de modo que la potencia se entregue a la carga y no se disipe en el transistor.

Conmutación con nFET

Un nFET (n-type field-effect transistor) puede utilizarse como un interruptor electrónico eficiente para controlar cargas desde un microcontrolador, como LEDs, motores o altavoces. En este contexto, se emplea comúnmente como un interruptor de lado bajo (low-side switch), donde el transistor conecta la carga a tierra.

En esta configuración, la carga se conecta al voltaje positivo (Vdd) y el drenador del transistor. La fuente del nFET se conecta a tierra, y la compuerta recibe la señal de control (por ejemplo, una señal PWM). Cuando la compuerta recibe suficiente tensión, el transistor conduce y permite el paso de corriente a través de la carga.

El comportamiento del nFET puede entenderse analizando sus dos estados principales:

Estado de apagado (OFF)

Cuando el transistor está apagado (Vgs bajo), presenta una resistencia muy alta entre drenador y fuente, por lo que prácticamente no circula corriente. En este estado, el consumo de potencia es mínimo, lo que hace a los FET muy eficientes.

Estado de encendido (ON)

Cuando el transistor está encendido (Vgs alto), la resistencia entre drenador y fuente es muy baja. Esta resistencia se denomina:

Ron = Vds / Id

Una resistencia baja implica una pequeña caída de tensión en el transistor, lo que reduce la disipación de potencia y permite que la mayor parte de la energía se entregue a la carga.

En aplicaciones reales, la resistencia de conducción depende de la tensión de compuerta. Por ejemplo, un transistor puede tener una resistencia de aproximadamente 11.9 mΩ a Vgs = 4.5 V y alrededor de 5.9 mΩ a Vgs = 10 V.

Los FETs de potencia se utilizan como interruptores debido a su alta eficiencia energética. En estado apagado, la corriente es muy baja, y en estado encendido, la caída de tensión es mínima. Sin embargo, durante la transición entre ambos estados, el transistor puede disipar potencia significativa.

Los dispositivos están disponibles en diferentes encapsulados (packages), como SOT-23, TO-92, TO-251 y TO-220, cada uno adecuado para distintos niveles de potencia y disipación térmica.

El pFET (p-type FET) funciona de manera similar al nFET, pero con polaridades invertidas. En este caso, la conducción ocurre cuando la tensión de compuerta es suficientemente negativa respecto a la fuente.

O sea, los FET son dispositivos ideales para conmutación debido a su baja disipación de potencia, alta eficiencia y capacidad de manejar corrientes elevadas. El objetivo en diseño es minimizar el tiempo en la región intermedia entre encendido y apagado, donde las pérdidas son mayores;

los FETs son componentes esenciales en la electrónica moderna debido a su capacidad de controlar corrientes mediante tensión, su alta eficiencia y su amplia aplicación en circuitos de potencia, amplificación y control.

Control de cargas y lógica con FET

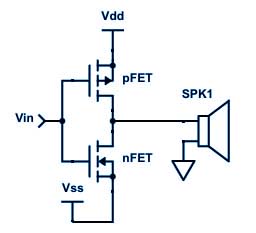

Figura . Una etapa de salida CMOS (CMOS output stage), compuesta por un pFET con su fuente conectada al riel de tensión positiva y un nFET con su fuente conectada al riel de tensión negativa, y cuya salida se obtiene de los drenadores conectados entre sí. Las fuentes (sources) (indicadas por las flechas centrales) están conectadas a los rieles de alimentación.

El otro terminal del altavoz (loudspeaker) se conecta a una tensión intermedia entre los rieles de alimentación, lo cual es fácil de lograr con una fuente de alimentación dual. Con una fuente simple, es más difícil generar una tensión intermedia capaz de suministrar las corrientes necesarias para un altavoz.

Los transistores FET se utilizan ampliamente para controlar cargas eléctricas desde sistemas digitales como microcontroladores. Debido a su alta eficiencia y baja disipación de potencia, son ideales para aplicaciones de conmutación.

En muchos casos, se emplean configuraciones de conmutación donde el FET actúa como un interruptor controlado por tensión. Sin embargo, cuando se trabaja con señales de control de bajo nivel, pueden surgir limitaciones relacionadas con el voltaje de compuerta (Vgs), especialmente si no es suficientemente alto para encender completamente el transistor.

Para resolver estos problemas, se utilizan diferentes estrategias, como el uso de resistencias pull-up y pull-down, que aseguran un estado definido en la compuerta cuando no hay señal activa.

Otra técnica común es el uso de inversores (inverters) basados en FET, que permiten adaptar niveles de señal y mejorar el control de la carga. Estos circuitos pueden presentar características no lineales, donde la transición entre estados no es instantánea.

El comportamiento de estos circuitos puede analizarse mediante curvas de transferencia, que relacionan la tensión de entrada con la tensión de salida. Estas curvas muestran cómo el circuito responde a diferentes niveles de señal.

En aplicaciones más complejas, se utilizan combinaciones de FETs para formar estructuras como:

- Interruptores bidireccionales.

- Puentes en H para control de motores.

- Circuitos de conmutación de alta eficiencia.

El uso de diodos internos (body diode) en los FETs es importante en aplicaciones con cargas inductivas, ya que permiten la circulación de corriente cuando el transistor se apaga, evitando picos de tensión peligrosos.

Además, en sistemas de conmutación rápida, es fundamental minimizar el tiempo en la región de transición entre encendido y apagado, ya que en esta zona el transistor puede disipar una cantidad significativa de energía.

En algunos casos, se emplean configuraciones con pFET y nFET combinados para lograr un control más eficiente, como en convertidores de potencia y circuitos de alimentación.

También es posible controlar dispositivos mediante señales moduladas en ancho de pulso (PWM), lo que permite regular la potencia entregada a la carga sin grandes pérdidas de energía.

Términos relacionados :

- Transistor MOSFET (Metal-Oxide-Semiconductor Field-Effect Transistor, MOSFET)

- Transistor de efecto de campo (Field-effect transistor, FET)

- Terminal de compuerta (Gate)

- Terminal de drenador (Drain)

- Terminal de fuente (Source)

- Tensión compuerta-fuente (Gate-to-source voltage, Vgs)

- Tensión drenador-fuente (Drain-to-source voltage, Vds)

- Corriente de drenador (Drain current, Id)

- Resistencia en conducción (On-resistance, Ron)

- Diodo interno (Body diode)

- Canal de conducción (Channel)

- Modo de enriquecimiento (Enhancement mode)

- Modo de agotamiento (Depletion mode)

- Transistor nMOS (n-channel MOSFET, nFET)

- Transistor pMOS (p-channel MOSFET, pFET)

- Óxido de compuerta (Gate oxide)

- Aislante de compuerta (Gate insulator)

- Capa epitaxial (Epitaxial layer)

- Sustrato (Substrate)

- Región N+ (N+ region)

- Región P (P region)

- Región de agotamiento (Depletion region)

- Conmutación de potencia (Power switching)

- Interruptor de lado bajo (Low-side switch)

- Interruptor de lado alto (High-side switch)

- Señal de modulación PWM (Pulse Width Modulation, PWM)

- Encapsulado TO-220 (TO-220 package)

- Encapsulado TO-92 (TO-92 package)

- Encapsulado SOT-23 (SOT-23 package)

- Encapsulado TO-251 (TO-251 package)

En resumen, los FET son elementos clave en la electrónica moderna para el control de cargas, permitiendo diseños eficientes, compactos y versátiles. Su correcta utilización requiere comprender tanto su comportamiento eléctrico como sus limitaciones prácticas.

|